24小(xiǎo)时联系電(diàn)话:18217114652、13661815404

中文(wén)

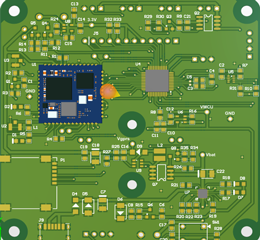

硬件开发

- PCB贴层设计要遵循的原则

相对于绝大多(duō)数的设计,PCB電(diàn)路板的性能(néng)需求、成本费用(yòng)、制造技术和系統的复杂度等关键因素存有(yǒu)不少相互间冲突的要求,PCB電(diàn)路板的叠层设计一般来说是在考量各个方面的关键因素后折中决定的。高速数字電(diàn)路和射频電(diàn)路一般来说都是采取多(duō)层板设计。

分(fēn)层

在多(duō)层PCB電(diàn)路板中,通常情况下含有(yǒu)有(yǒu)的信号、電(diàn)源平面和接地平面。電(diàn)源平面和接地平面一般而言是没有(yǒu)分(fēn)割的实體(tǐ)平面。它们之间将為(wèi)相互邻近的信号走線(xiàn)的電(diàn)流提供了一个好的低阻抗的電(diàn)流返回路径。

信号层绝大部分(fēn)处在这类電(diàn)源或地参考平面层之间,形成对称带状線(xiàn)或非对称带状線(xiàn)。多(duō)层PCB電(diàn)路板的顶层和底层一般来说应用(yòng)于防止元器件和少量的走線(xiàn),这类的信号的走線(xiàn)要求不可(kě)过長(cháng),以减低走線(xiàn)带来的直接辐射。

确定单電(diàn)源参考平面

安 全使用(yòng)去耦電(diàn)容是处理(lǐ)電(diàn)源完整性的一种至关重要的措施。去偶電(diàn)容只能(néng)够存放在PCB的顶层和底层。

去耦電(diàn)容的走線(xiàn)、焊盘,还有(yǒu)过孔将严重的影响到去耦電(diàn)容的效果。因此在设计时必须充分(fēn)考虑连接去耦電(diàn)容的走線(xiàn),应尽可(kě)能(néng)的短而宽,连接到过孔的导線(xiàn)也应尽可(kě)能(néng)的短。

确定多(duō)電(diàn)源参考平面

多(duō)電(diàn)源参考平面将被拆分(fēn)成好几个電(diàn)压不相同的实體(tǐ)區(qū)域。倘若紧邻多(duō)電(diàn)源层的是信号层,那其附近的信号层上的信号電(diàn)流,有(yǒu)可(kě)能(néng)会遭到不满意的返回路径,使返回路径上产生缝隙。

相对于高速数字信号,这些不合理(lǐ)的返回路径设计也许会造成情况严重的问题,因此要求高速数字信号布線(xiàn)需要遠(yuǎn)离多(duō)電(diàn)源参考平面。

确定多(duō)个接地参考平面

众多(duō)接地参考平面能(néng)造成其中一种好的低阻抗的電(diàn)流返回路径,能(néng)很(hěn)大程度上减少共模EMI。

接地平面和電(diàn)源平面须要紧密耦合,信号层也要和紧邻的参考平面紧密耦合。减少层与层之间的介质厚度,以便于实现这个目的。

合理(lǐ)设计布線(xiàn)组合

一种信号路径所跨跃的两种层次為(wèi)一种【布線(xiàn)组合】。蕞适合的布線(xiàn)组合设计是尽量避免返回電(diàn)流,从一种参考平面流到另一种参考平面;而是从一种参考平面的一个点(面)留到另一个点(面)。

而為(wèi)了能(néng)实现复杂的布線(xiàn),走線(xiàn)的层间转换是无法避免的。在信号层间转变时,要确保返回電(diàn)流可(kě)以顺利地从一种参考平面流到另一种参考平面。

以上是我对“PCB贴层设计要遵循的原则”的介绍,提供给大家参考。

在線(xiàn)询价

- *

- *

- *

- *

- *

-

*