24小(xiǎo)时联系電(diàn)话:18217114652、13661815404

中文(wén)

- 您当前的位置:

- 首页>

- 電(diàn)子资讯>

- 技术专题>

- 旁路和去耦電(diàn)容器放置...

技术专题

旁路和去耦電(diàn)容器放置准则

通常从電(diàn)源的角度来看電(diàn)源完整性问题,但是查看IC的输出同样重要。去耦電(diàn)容和旁路電(diàn)容旨在补偿PDN上出现的功率波动,从而确保信号電(diàn)平一致,并在IC的電(diàn)源/接地引脚上看到恒定電(diàn)压。我们已经汇编了一些重要的旁路和去耦電(diàn)容器放置准则,以帮助您在下一个PCB中成功使用(yòng)这些组件。

两个相关的電(diàn)源完整性问题

去耦電(diàn)容器和旁路電(diàn)容器用(yòng)于解决两个不同的電(diàn)源完整性问题。尽管这些電(diàn)源完整性问题是相关的,但它们以不同的方式表现出来。要注意的第一点是,术语“去耦電(diàn)容器”和“旁路電(diàn)容器”在用(yòng)于電(diàn)源完整性时是错误的。他(tā)们不会解耦或绕过任何东西。它们也不会将“噪音”传递给地面。它们只是随时间推移进行充電(diàn)和放電(diàn),以补偿噪声波动。这些术语将这些電(diàn)容器的功能(néng)称為(wèi)電(diàn)源完整性策略的一部分(fēn)。

首先,考虑去耦電(diàn)容器。一般说来,去耦電(diàn)容器的目的是确保電(diàn)源轨/接地层和接地层之间的電(diàn)压保持恒定,以抵抗低频電(diàn)源噪声,PDN上的振铃以及PDN上的任何其他(tā)電(diàn)压波动。当放置在電(diàn)源和接地平面之间时,去耦電(diàn)容器与这些平面并联,这会增加总的PDN電(diàn)容。实际上,它们补偿了平面间電(diàn)容不足,并降低了PDN阻抗,从而使PDN電(diàn)压中的任何振铃极小(xiǎo)化。

现在考虑使用(yòng)旁路電(diàn)容器。它们还旨在在PDN和驱动IC内保持恒定電(diàn)压,但是它们所补偿的電(diàn)压在输出引脚和PCB接地层之间。尽管它们放置在電(diàn)源引脚和IC上的接地之间,但它们执行的功能(néng)是不同的,以防止接地反弹。当数字IC切换时,键合線(xiàn),封装和引脚中的寄生電(diàn)感会导致驱动器输出和地之间的電(diàn)压增加。旁路電(diàn)容器输出的電(diàn)压指向与地面反弹電(diàn)压相反的位置,理(lǐ)想情况下,使总電(diàn)压波动之和為(wèi)零。

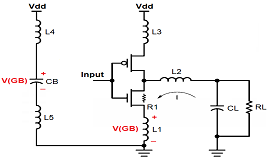

在以上模型中,存在一个闭环,该闭环包括旁路電(diàn)容器(CB)和IC封装/接地连接上的杂散電(diàn)感L1。请注意,在输出引脚和接地层之间测量了接地反弹電(diàn)压 V(GB)。其余的電(diàn)感都是寄生電(diàn)容,会影响旁路電(diàn)容器的响应时间以补偿接地反弹。在理(lǐ)想模型中,旁路電(diàn)容器看到的電(diàn)压将补偿开关期间杂散電(diàn)感器L1产生的接地反弹電(diàn)压。

旁路電(diàn)容器放置准则

如果您看一下接地反弹的发生方式,那么应该在哪里放置旁路電(diàn)容器应该很(hěn)明显。由于上述電(diàn)路模型中的寄生電(diàn)感,应将旁路電(diàn)容器放置在尽可(kě)能(néng)靠近電(diàn)源和接地引脚的位置,以极大程度地减小(xiǎo)这些電(diàn)感。这与您在许多(duō)应用(yòng)筆(bǐ)记和组件数据手册中找到的建议是一致的。

关于寄生電(diàn)感,还有(yǒu)一个方面需要考虑,那就是如何将连接路由到IC。您应该通过过孔将電(diàn)容器直接连接到接地层和電(diàn)源层,而不是从電(diàn)容器到IC引脚走一条短走線(xiàn)。确保符合此布置中的焊盘和走線(xiàn)间距要求。

為(wèi)什么会这样呢(ne)?原因是接地/電(diàn)源平面布置(只要这些平面位于相邻层中)将具有(yǒu)非常低的寄生電(diàn)感。实际上,这是電(diàn)路板上寄生電(diàn)感的最低来源。如果您可(kě)以将旁路電(diàn)容器放在電(diàn)路板的底部,则可(kě)以实现更好的布置。

去耦電(diàn)容器放置准则

确定PDN中所需的去耦電(diàn)容器的尺寸后,需要将其放置在某处,以确保它可(kě)以补偿输入電(diàn)压波动。实际上,最好使用(yòng)多(duō)个去耦電(diàn)容器,因為(wèi)它们将并联排列,并且并联排列将提供较低的有(yǒu)效串联電(diàn)感。

较早的准则会指出,您可(kě)以在板上的任何地方放置去耦電(diàn)容器。但是,请注意这一点,因為(wèi)这会增加去耦電(diàn)容器和目标IC之间的寄生電(diàn)感,从而增加PDN阻抗和对EMI的敏感性。相反,对于具有(yǒu)快速边沿速率的IC,应将去耦電(diàn)容器放置在靠近目标IC的位置。下图显示了IC附近的典型旁路和去耦電(diàn)容器布置。这是高速電(diàn)路的一种很(hěn)好配置,因為(wèi)对于所有(yǒu)信号路径,電(diàn)容器和IC之间的寄生電(diàn)感非常低。

小(xiǎo)心建模PDN阻抗

请记住,PDN阻抗决定了PDN上任何瞬态電(diàn)压振铃的大小(xiǎo)(在電(diàn)源和地之间测得)。但是,旁路電(diàn)容器也连接在電(diàn)源和地之间,因此它们也是PDN的一部分(fēn)!旁路和去耦電(diàn)容器以及寄生電(diàn)容和電(diàn)感将共同决定PDN的阻抗谱,从而形成复杂的谐振和反谐振结构。

虽然您可(kě)以在線(xiàn)找到一些PDN优化工具,但它们假定所有(yǒu)寄生電(diàn)路元素均為(wèi)零,这与实际情况不符。在電(diàn)路模型中,如何布置去耦/旁路電(diàn)容器(小(xiǎo)到大或大到小(xiǎo))都无关紧要。在实际布局中,寄生因素很(hěn)重要(如上所述),特别是对于高速/低電(diàn)平IC。